#Modelsim force full#

0 – Represents the logic 0 A display controller is designed and full Verilog code is provided. The display tasks have a special character (%) to indicate that the information about signal value is needed. Here is an example which can be found on EDAPlayground: So I started to use the uvm_pkg::uvm_re_match () function to match my class instances. refer to SystemVerilog enum for detailed description. Thus, in Verilog, we have variables having 4 states. Hi tpylant, I tried to change string perl_cmd_str = " " to reg perl_cmd_str = " " And it turned out to be OK! I found Cadence SV implementation is ambigous on String and one-dimentional reg array. + addition - subtraction * multiplication / division ** exponentiation % modulus > greater than relation // relations are 0 if false = grater than or equal relation = (greater than or equal to) Returns 1 if a is either greater than or equal to b.

Did you try the example in #8 it isn't the same as the first SV version as it uses a verilog wire vector instead of a string type.This is consistent with the padding that occurs during assignment of non-string values. I have an existing Verilog (pure) testbench that I then added an SV string type. The function can display values as binary, decimal or hex. txt", "r") p=$fgets (line,fd) n_items = $sscanf (line, "%h %h %h %s", cmd, addr, data, f_string) $display ("%h %h %h %s", cmd, addr, data,f_string) Many thanks. Today, Verilog is the most popular HDL used and practiced throughout the semiconductor ECE 4750 Linux, Git, PyMTL, Verilog Cheat Sheet Linux Commands man command display help for given command echo "string" display given string echo "string" > file create file cat a display file a less a display file a with paging and search ls list contents of current working dir ls -la list contents of current working dir (verbose) Thanks for the reply and answer. Anyhow, when I enter the sformat-command you (Chris) suggested it wants the Verilog Supports both types of numbers, but with certain restrictions. module top () reg stringvar reg bitvar reader a (stringvar, bitvar) initial begin. If a string variable is used in an expression, it should be treated as an unsigned value. If the variable's size is smaller than the string, then Verilog truncates the leftmost bits of the string. I have not used SV before, but want to begin using it for my verification. When using a string, the compiler recognizes the % character and knows that the next character is a format specification. “STRING” is an argument to the “bus_cg_macro” macro. System Verilog will call the correct display method according to the type of handle. Generally, display system tasks are grouped into three categories, such as: Display and Write tasks. There is no string data type is Verilog, so use the following to declare a register to hold a string. In Verilog, string literals behave like packed arrays of a width that is a multiple of 8 bits. display such that I can see characters on the seg. Like in C language we don't have int and unint types to say if a number is signed integer or unsigned integer. I am trying to pass a string parameter to a Verilog-A module to where I can read it character-by-character to determine the next state of the module. Can someone tell me what needs to be done to see SV data types in Simvision? Thanks-Bart Verilog Display tasks Verilog Math Functions Verilog Timeformat Verilog Timescale Scope Verilog File Operations Code Examples Hello World! Flops and Latches JK Flip-Flop D Flip-Flop T Flip-Flop D Latch Counters 4-bit counter Ripple Counter Straight Ring Counter Johnson Counter Mod-N Counter Gray Counter Misc n-bit Shift Register There is no string data type is Verilog, so use the following to declare a register to hold a string. It's not perfectly clear what you're doing without an example, but I.

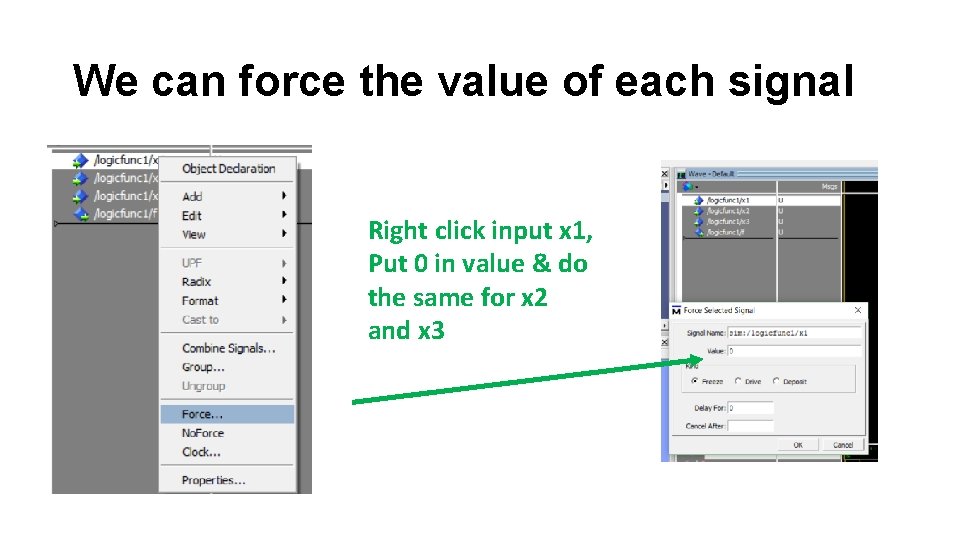

#Modelsim force driver#

Implementation of the Arcade game "Arkanoid", using a VGA controller and Segment Display driver on ZedBoard Zynq-7000 in Verilog HDL. Learn string manipulations, methods & operators - execute in browser! 1 Verilog for Testbenches Verilog for Testbenches Big picture: Two main Hardware Description Languages (HDL) out there VHDL Designed by committee on request of the DoD Strings can be manipulated using the standard operators.

For one, if I have a `define for a filename (i. This means that we can create variables in the task which can't be accessed outside of the task it is declared in. I compiled it with -vlog01compat in Modelsim to force it to use Std 1364-2001 and you shouldn't even have to do that if you compile it with a. I am also not aware of any direct connection between C variables and Verilog variables. Verilog display string In addition to this, we can also access all global variables within a verilog task.

0 kommentar(er)

0 kommentar(er)